LLMs in EDA: Designing Chips with Language Models

In 2025, Language Models aren’t just writing code—they’re co-designing silicon. From RTL generation to verification, LLMs are transforming Electronic Design Automation (EDA) workflows with speed, accuracy, and intelligence that’s redefining how chips are built.

🧩 What is EDA, and Why Does It Matter?

Electronic Design Automation (EDA) refers to the suite of tools used to design, verify, and test integrated circuits (ICs), chips, and system-on-chips (SoCs).

Traditionally, EDA involves:

- HDL (Hardware Description Language) programming (e.g. Verilog, VHDL)

- Synthesis (translating code to gate-level logic)

- Place & Route (mapping gates onto chip layout)

- Verification & Validation

- Simulation & Timing analysis

These are highly complex, error-prone, and expensive processes requiring deep domain expertise.

🤖 Enter LLMs: A New Era for Chip Design

Large Language Models like GPT-4, Claude, and Gemini are now being fine-tuned or integrated into EDA workflows for:

| Task | LLM Role |

|---|---|

| 🧬 HDL generation | Generate Verilog/VHDL from natural language or high-level specs |

| 🧪 Formal verification | Suggest assertions and testbenches |

| 🧠 RTL refactoring | Optimize, simplify or comment legacy RTL code |

| 📏 Floorplanning assistance | Provide placement heuristics or interpret constraints |

| 💬 Design documentation | Generate specs, summaries, comments automatically |

| 🤝 EDA tool scripting | Auto-write TCL scripts, Python hooks for tools like Synopsys, Cadence |

🔍 Use Case 1: Generating RTL from Natural Language

Prompt:

“Design a 4-bit synchronous up-counter with reset in Verilog.”

LLM Output (GPT-4):

verilogCopyEditmodule up_counter (

input clk,

input reset,

output reg [3:0] count

);

always @(posedge clk or posedge reset) begin

if (reset)

count <= 4'b0000;

else

count <= count + 1;

end

endmodule

🔍 Use Case 2: Bug Hunting & Testbench Creation

LLMs can:

- Auto-create assertions to verify conditions

- Generate SystemVerilog testbenches

- Simulate corner cases from spec interpretation

This dramatically reduces verification time, which can consume 50–70% of total chip development effort.

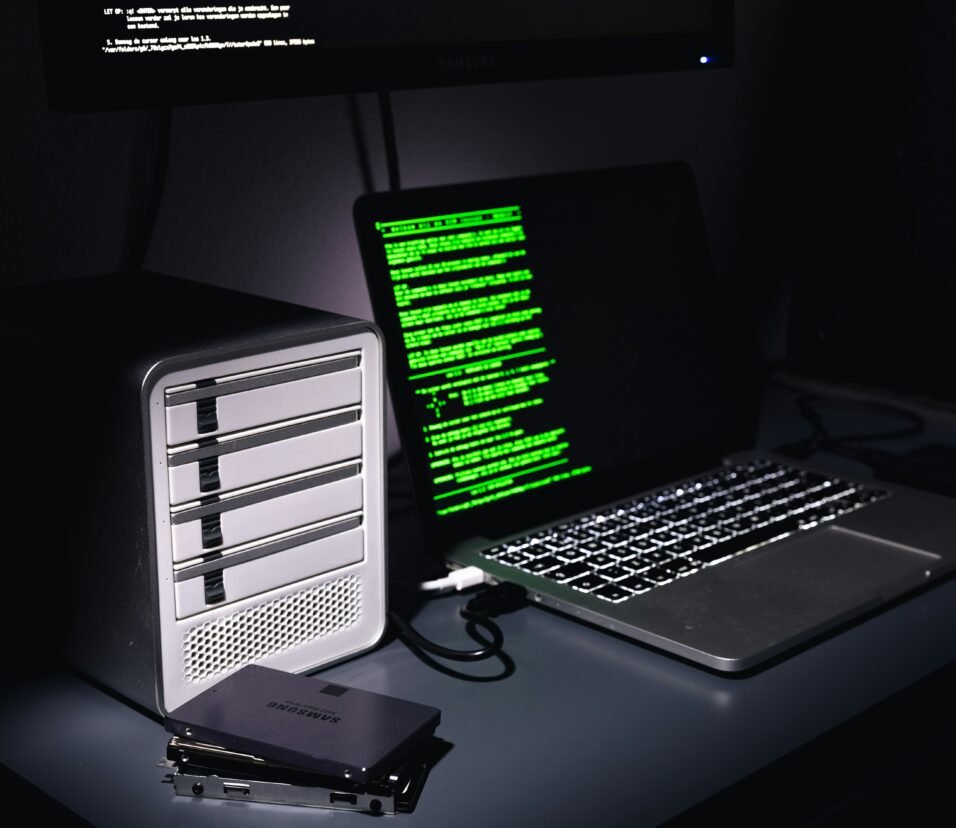

🔍 Use Case 3: Interfacing with EDA Tools

LLMs can help:

- Generate TCL commands for Synopsys/Primetime

- Write Python automation for Cadence workflows

- Extract meaningful insights from timing reports

- Detect layout violations or suggest fixes (using tool API outputs)

Combined with agentic AI, these models can soon:

- Run tools

- Parse results

- Suggest next steps autonomously

⚡ Current Limitations

| Challenge | Notes |

|---|---|

| ❌ Lack of deep domain logic | LLMs struggle with advanced async logic or multi-clock domains |

| 📉 Accuracy risk | Hallucinated HDL can produce subtle, dangerous bugs |

| ⚠️ Tool-specific quirks | EDA tools often have proprietary behaviors and file formats |

| 🔐 Data sensitivity | Models need secure environments for handling IPs and designs |

| 🧠 Limited contextual memory | Complex chip designs span multiple files/modules beyond current LLM context limits |

🛠️ Who’s Leading the LLM+EDA Frontier?

| Company | Contribution |

|---|---|

| Synopsys | Integrating LLMs for RTL analysis & debug |

| Cadence | Generative-AI assistants in custom IC design |

| Using internal LLMs to improve TPU design cycles | |

| Intel | Auto-generating hardware IP libraries with LLM pipelines |

| Tenstorrent / SambaNova | Using LLMs for hardware/software co-optimization |

| Open-source | Projects like EDA-GPT and HDL-generating copilots emerging on GitHub |

🔮 The Future: LLMs as Silicon Architects?

By 2027, expect:

- Full-stack EDA copilots that understand everything from spec to layout

- Design agents that coordinate RTL, layout, simulation, and testbench cycles

- Simulation-integrated LLMs that read waveform outputs and suggest logic fixes

- Prompt-native chip design, where users describe a function and the AI builds HDL, constraints, docs, and tests

✅ TL;DR – LLMs in EDA

| Aspect | Summary |

|---|---|

| What | Use of large language models to generate, verify, and automate chip design |

| Why it matters | Speeds up RTL writing, reduces verification time, lowers entry barrier |

| Use Cases | HDL generation, testbenches, scripting, floorplanning, documentation |

| Challenges | Accuracy, security, multi-file context, deep logic understanding |

| Future | Agentic AI for end-to-end chip design pipelines |

📣 Final Thoughts: A New Silicon Renaissance

With LLMs entering the EDA ecosystem, we’re seeing a convergence of natural language and hardware logic.

- Chip designers can now speak to silicon

- EDA workflows are becoming smarter and faster

- And hardware innovation is no longer gated by steep syntax learning curves